### MASTER OSCILLATOR

The frequency of the master oscillator is determined by the contents of several output ports. Port 10H sets the master frequency. It is given by the following formula:

If bit 4 of output port 15H is set to 1, the master oscillator frequency will be modulated by notice. The amount of modulation will be set by the 8-bit pose volume register, output port 17H.

If bit 4 of output port 15H is set to  $\emptyset$ , the frequency of the master oscillator will be modulated by a constant value to give a vibrato effect. The amount of modulation will be set by the vibrato depth register (the first 6 bits of output port 14H). The speed of modulation is set by the vibrato speed register (upper 2 bits of output port 14H);  $\emptyset\emptyset$  for fastest and 11 for slowest.

Frequency modulation is accomplished by adding condulation value to the contents of port the and sending the result to the master oscillator frequency generate. In noise modulation, the modulation value is an 8-bit word from the noise generator. If a bit in the noise volume register is set to, the corresponding bit in the modulation value word will be set 40. In vibrato modulation, the modulation value alternates between 4 and the contents of the vibrato volume register.

Modulation can be completely disabled by setting the master volume to  $\emptyset$  if noise modulation is being used, or by setting the vibrato depth to  $\emptyset$  when vibrato is used.

### TONES

The system contains three tone generators each clocked by the same master oscillator. The frequency of Tone A is set by output port 11H, Tone B by output port 12H, and Tone C by output port 13H. The frequency is given by the following formula:

$F_{1} = \frac{F_{m}}{2 \text{ (contents of TONE PORT+1)}} = \frac{894}{(PORT 10H+1) \text{ (contents of TONE PORT+1)}} Khz$

The tone volumes are controlled by output ports 15H and 16H. The lower 4 bits of port 16H set Tone A Volume, the opper 4 bits sets Tone B Volume. The lower 4 bits of port 15H sets Tone C Volume. Noise can be mixed with the tones by setting bit 5 of port 15H to 1. In this case the noise volume is given by the apper 4 bits of port 17H. In all cases a volume of 4 is silence and a volume of 4 is loudest.

SOUND BLOCK TRANSEER

All 8 bytes of sound control can be sent to the audio circuit with one OTIR instruction. Register C should be sent to 18H, register B to 8H and HL porting to the sortes of data. The data pointed to by HL goes to port 7H and the next 7 bytes of data goes to ports 16H through 10H.

17H Data-to-port HL -> Memory Location χ 16H X+1Data-to-port 15H χ+2 Data-to-port 14H X+3Data-to-port X+4 Data-to-port 13H 12H X+5 Data-to-port 11H X+6 Data-to-port

X+7 Data-to-port 10H

# OUTPUT PORTS

| PORT NUMBER |             | FUNCTION                                       |

|-------------|-------------|------------------------------------------------|

| ØН          |             | Color Register Ø                               |

| 1H          |             | Color Register 1                               |

| 2H          |             | Color Register 2                               |

| 3H          |             | Color Register 3                               |

| 4H          | 2           | Color Register 4                               |

| 5H          | <b>F</b>    | Color <b>K</b> egister 5                       |

| 6Н          | 3           | Color egister 6                                |

| 7H          | Ş           | Color Register 7                               |

| 8H          |             | Low/High Resolution                            |

| 9Н          | NFORMATION  | Horizontal Color Bourdary,<br>Background Color |

| АН          | 2           | Vertical Blank Register                        |

| ВН          |             | Color Block Transfer                           |

| СН          | <b>&gt;</b> | Magic Register                                 |

| DH          | $\alpha$    | Interropt Feedback Register                    |

| EH          | ROPRIE TARY | Interport Enable and Hode                      |

| FH          |             | Interrupt Line                                 |

| 1ØH         | IE          | Master Oscillator                              |

| 11H         | Œ           | Tone Frequency                                 |

| 12H         | σ           | Tone B Frequency                               |

| 13H         | $\sim$      | Tone C Frequency                               |

| 14H         | 7           | Vibrato Register                               |

| 15H         | •           | Tone C Volume, Noise                           |

|             |             | Modulation Control                             |

| 16H         |             | Tone A Volume, Tone B Volume                   |

| 17H         |             | Noise Volume Register                          |

| 18H         |             | Sound Block Transfer                           |

| 19H         |             | Expand Register                                |

|             |             |                                                |

# INPUT PORTS

| PORT NUMBER                                                     |                          | FUNCTION                                                                                                                                                                                                                      |

|-----------------------------------------------------------------|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8H<br>EH<br>FH<br>1ØH<br>11H<br>12H<br>13H<br>14H<br>15H<br>16H | PROPRIE TARY INFORMATION | Intercept Feedback  Vertical Line Feedback  Horizontal Address Feedback  Player 1 Handle  Player 2 Handle  Player 3 Handle  Player 4 Handle  Keypad Solumn 0 (rioc)  Keypad Solumn 1  Keypad Solumn 2  Keypad Solumn 3 (left) |

|                                                                 | PROPRIE TARY             | Dave Sutting  DO NOT F                                                                                                                                                                                                        |

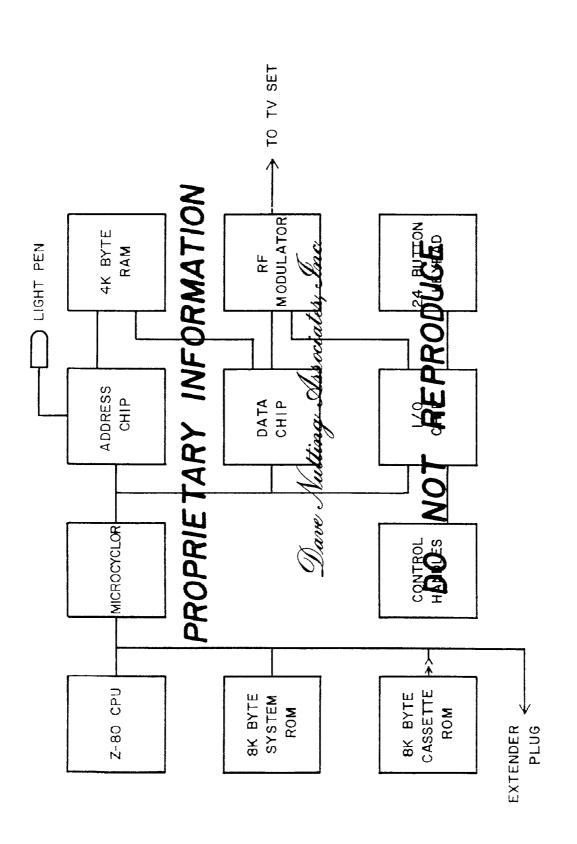

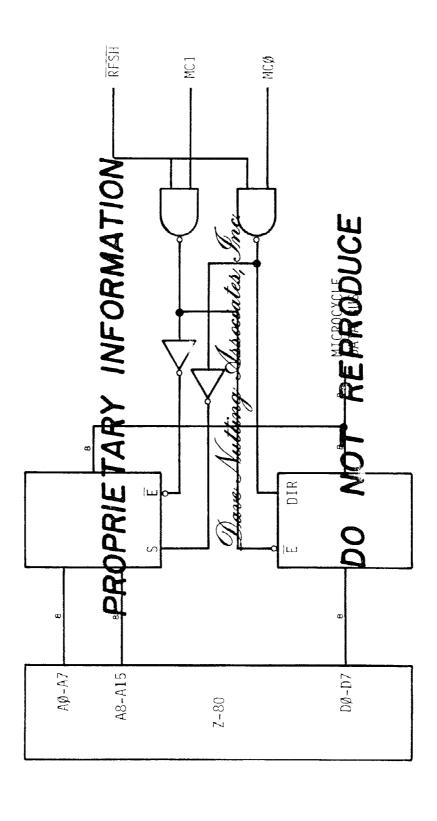

### MICROCYCLER

The purpose of the microcycler is to combine the 16-bit Address Bus and the 8-bit Data Bus from the Z-80 into one 8-bit Microcycle Data Bus to the Data Chip, Address Chip, and I/O Chip. This was done to reduce the pin count on the components.

The Microcycle Data Bus can be in any of four modes. Its mode is controlled by MCØ and War coming from the Data Chip and  $\overline{\text{RFSH}}$  from the Z-8Ø. The modes are shown below.

|      |     | $\mathbf{L}$ |                           |

|------|-----|--------------|---------------------------|

| RFSH | MCØ | MCO          | Microc≤ Data Bus Contents |

|      |     | H            | § Œ                       |

| Ø    | Ø   | $\emptyset$  | AØ - 🔀 from Z-8Ø          |

| Ø    | Ø   | 1            | AØ - AZ from Z-8Ø         |

| Ø    | 1   | Ø            | AØ - AB From Z-8Ø         |

| Ø    | 1   | 100          | AØ – Æ from Z-8Ø          |

| 1    | Ø   | $\emptyset$  | AØ - AB from Z-8Ø         |

| 1    | Ø   | 1            | A8 - A15 from Z-80        |

| 1    | 1   | Ø            | DØ – D≷from Z–8Ø          |

| 1    | 1   | 1            | DØ - 😿 to Z-8Ø            |

|      |     | <u>o</u>     | 9                         |

MCØ and MC1 change 140 sec after the rising edge of  $\underline{\Phi}$ . Their changes are shown in the timin diagrams of various instruction cycles.

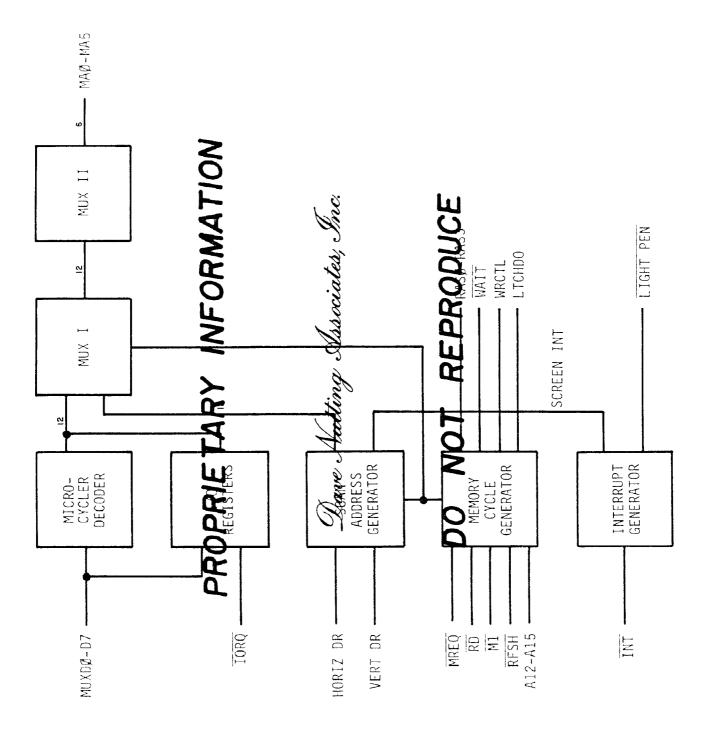

### ADDRESS CHIP DESCRIPTION

The Microcycle Decoder generates twelve bits of Z-8Ø address from the 8-bit Microcycle Data Bus. This address is then fed through MUX I and MUX II to MAØ-5 which go to the RAM. The Scan Address Generator generates a 12-bit address which is used to read video data from the RAM. This address goe from Ø to FFFH once every frame (1/60 sec.).

MUX I sends either the Gran Address of 3-80 Address to its 12 outputs. An output of the Scan Address Generator controls MUX I If the Scan Address Generator and the Z-80 request memory cycle it the same time, the Scan Address Generator will have higher priority of the Z-80 will be required to wait (by the WAIT output). The Scan Address Generator never requires the memory for more than one consecutive memory cycle, so the Z-80 is never required to wait for the memory for more than one cycle. HORIZ DR and VEXT DR synchronize the Scan Address Generator with the Data Chip and the TV Scan.

The purpose of MUX II is to multiplex its 12 inputs to the six address bits in the two time slaves required for  $4K \times 1$  16 pin RAMS.

The Memory Cycle General controls memory cycles generated by either the Z-8 $\emptyset$  or Scan Address Generate  $\overline{\text{MREQ}}$ ,  $\overline{\text{RD}}$ ,  $\overline{\text{MI}}$ ,  $\overline{\text{RFSH}}$ , and A12-A15 are from the Z-8 $\emptyset$ . A12-A15 are fed a rectly from the Z-8 $\emptyset$  because if they were brought out of the microcycle decoder, they would arrive too late in the memory cycle. The RAS $\emptyset$  - RAS3 outputs are used to activate memory cycles. In the consumer game, only RAS $\emptyset$  is used to one bank of RAM (4K x 8). In the commercial game, all four RAS's are used to control four banks of RAM (16K x 8). WRCTL and LTCHDO are control signals to the Data Chip. WRCTL tells the Data Chip when to place data to be written to memory on the memory data bus. LTCHDO tells the Data Chip when valid data from RAM is present on the memory data bus.

As mentioned earlier,  $\overline{\text{WAIT}}$  is generated when the Z-80 and Scan Address Generator both request memory at the same time.  $\overline{\text{WAIT}}$  is also generated for one cycle every time the Z-80 requests a memory access, even if there is no conflict with the scan Address. This is because the microcycler slows down Z-80 memory accesses. The Z-80 address bus and data bus must time share the microcycle bus so the Z-80 data reaches the microcycle bus very late in the memory cycle.

The INT Generator generates two types of interrupts to the Z-80; Light Pen and Screen interrupts. A screen interrupt is generated when screen interrupts are enabled and the TV scan completes a contain line on the screen (from 0 to 255). The line at which the interrupt will occur is determined by the Z-80. This interrupt can be used for timing since the TV rescans every line since every 1/60 sec. A light pen interrupt occurs when the light pen interrupt is enabled and  $\overline{\text{LIGHT PEN}}$  goes low. The current scan address is laved in latent in the Scandidress Generator. The Z-80 can read the contents of these latches to desirmine the scan address at the time  $\overline{\text{LIGHT PEN}}$  was activated and thus the position of the light pen on the screen.

The I/O Decode circuit  $\alpha$  used during Z-8Ø input and output instructions. Z-8Ø input instructions are used to read the scan address after light pen interrupts. Output instructions are used to enable the two interrupts and set the line number for screen interrupts.

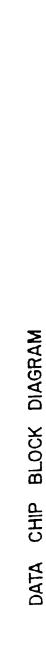

### DATA CHIP DESCRIPTION

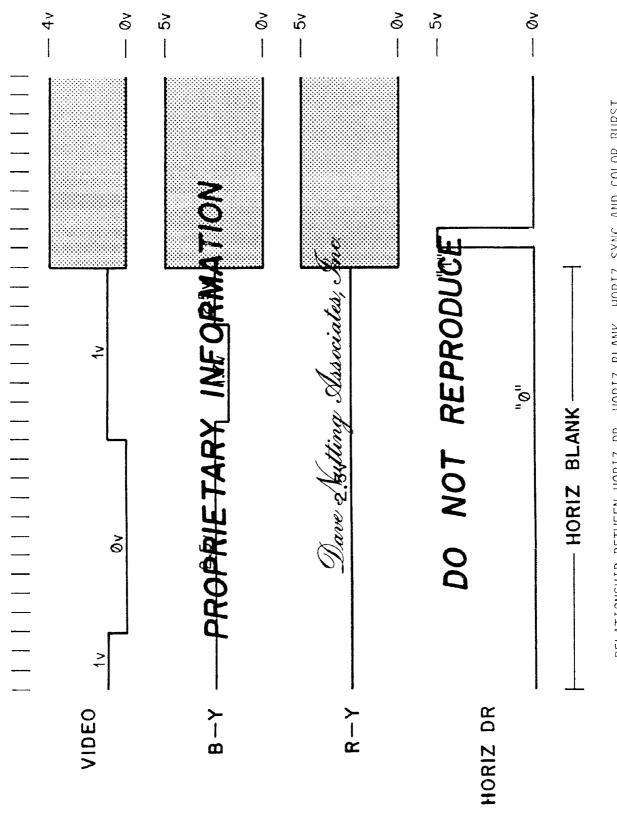

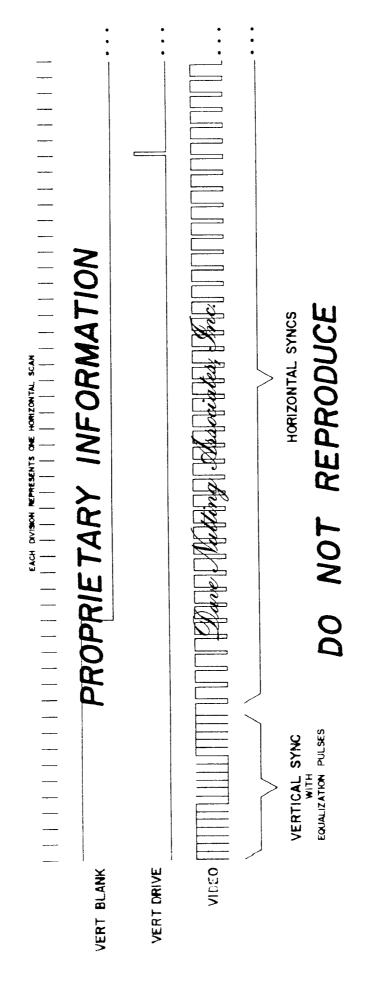

The TV Sync Generator uses 7M and  $\overline{7M}$  (7.159090 Mhz square waves) to generate NTSC standard sync and blank to be sent to the Video Generator. It also generates HORIZ DR and VERT DR for synchronization with the Address Chip. HORIZ DR occurs once every horizontal line (63.5 usec), and VERT DR occurs once every frame (16.6 msec).

The Shift Register load parallel data from the memory data bus (MDØ - MD7) and shifts it out of it two serial outputs. The TV sync Generator controls when data is loaded or wrifted. In a consumer game, in two outputs of the shift register are sent through MUX I to MUX II. On a commercial game, SERIAL Ø and SER UL 1 are sent through the MUX to MUX II. The two bits from MUX I select 8 bits to be sent through MUX II to the Video Generator. These 8 bits then determine the analog values of VIDEO, R-Y, and B-Y. 2.5V is a 2.5 D C reference avel.

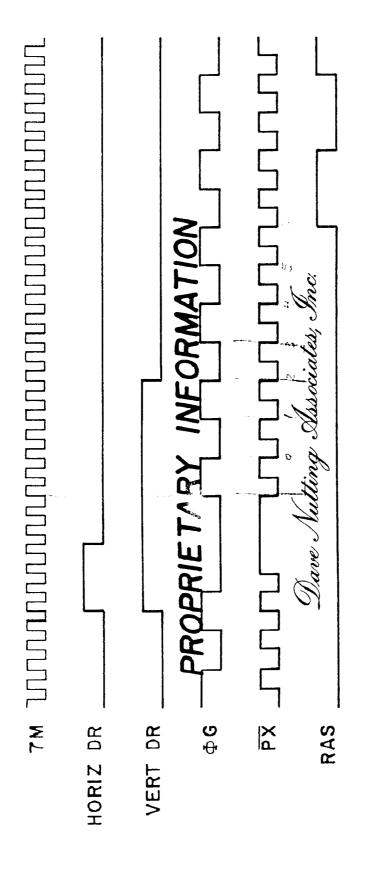

The Clock Generator generates  $\emptyset G$  and  $\overline{PX}$  from 7M. These are the clocks for the rest of the system. The frequency of  $\overline{PX}$  is half that of 7M and the frequency of  $\emptyset G$  is half that of  $\overline{PX}$ .

The Microcycle Generator generates the microcycle corrol bits, MCØ and MC1, from  $\overline{IORQ}$ ,  $\overline{MREQ}$ ,  $\overline{R}$  and  $\overline{M1}$ , all from the Z-8Ø.

In memory write cycles WRCTL is activated and the Memory Control circuit generates  $\overline{\text{DATEN}}$ . The Magic Function Generator takes the data from the Z-8Ø on MUXDØ - D7 and transfers it to MDØ - MD7. If a Magic write is being done, the Magic Function Generator will modify the data as required before it places it on the memory data bus.

A Magic write is a memory write cycle in which data is written to a location, (X) from  $\emptyset$  to 16K. All memory from  $\emptyset$  to 16K is ROM and cannot be modified. The data is modified by the Magic Function Generator and is written to location  $\longrightarrow$  16K. The way in which the data is modified is determined by the 7 bis coming from the I/O registers.

In memory reads, data in transferred (x2m MDØ - MD7 to MUXDØ - MUXD7.

Also, LTCHDO is activate which causes the data from AM to be latched up in a register in the Magic Function, generator. To latched data is used in some magic functions.

The I/O registers are  $\mathbb{Z}_{2}$  and  $\mathbb{Z}_{3}$  in the Address Chip.

**PROPRIETARY**

FON

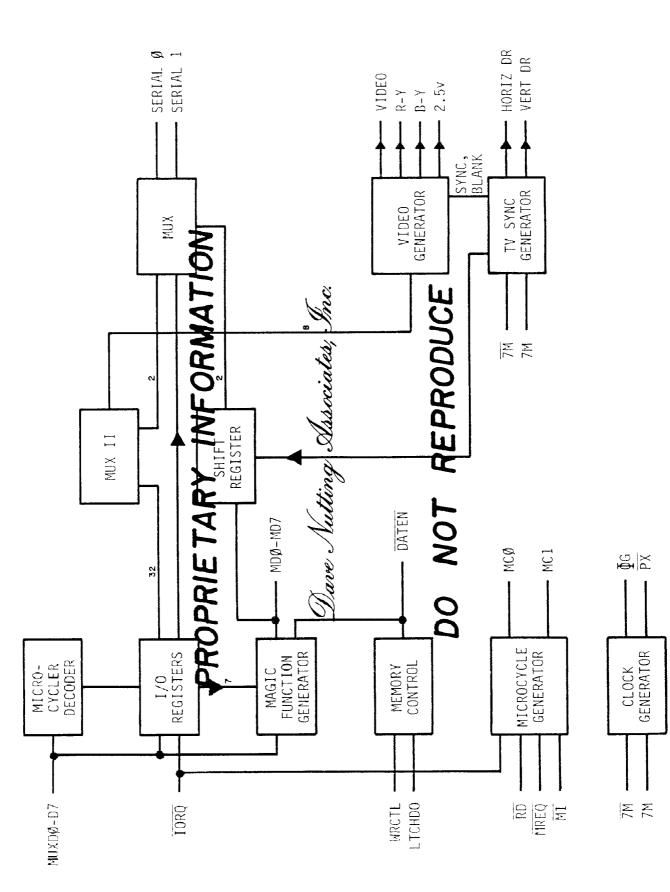

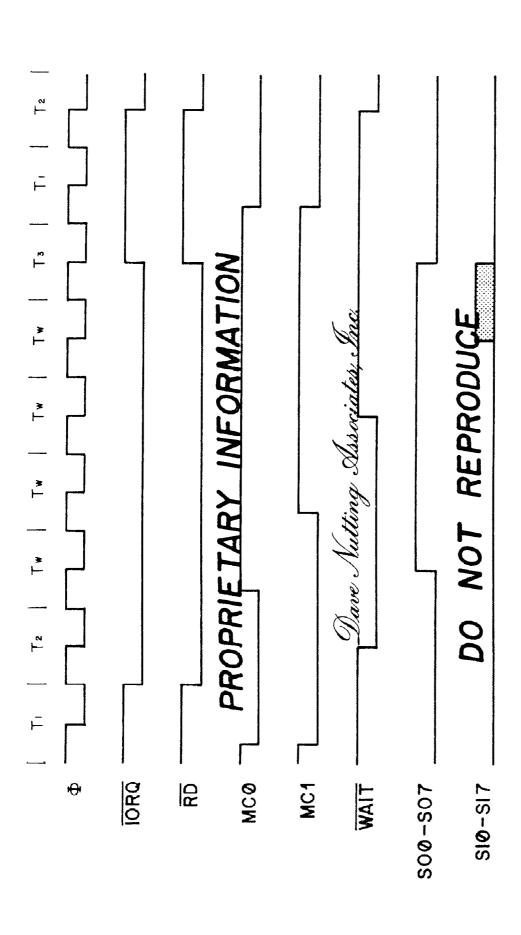

### I/O CHIP DESCRIPTION

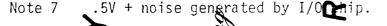

The Z-8Ø communicates with the I/O Chip through input and output instructions. The state of an 8 x 8 switch matrix can be read through the Switch Scan circuit. When an input instruction is executed, one of the SOØ-SO7 lines will be activated. When a line is activated, the switch matrix will feed back eight bits of data on SIØ-SI7. This data is in turn fed to the Z 8Ø through MUXDØ, - MUXD7.

The Z-80 can read the position of four potentiometers (ots) through the A-D Converter circuit. The pots are continuously scalar d by the A-D Converter and the result of the convergions are stored in a RAM in the A-D Converter circuit. The Z-80 simply reads this RAM with input instructions.

The Z-8Ø loads data into the Music Processor with output instructions. This data determines the Characteristic of the audio that is generated. The Music Processor is described in detail below.

PROPRIET

00

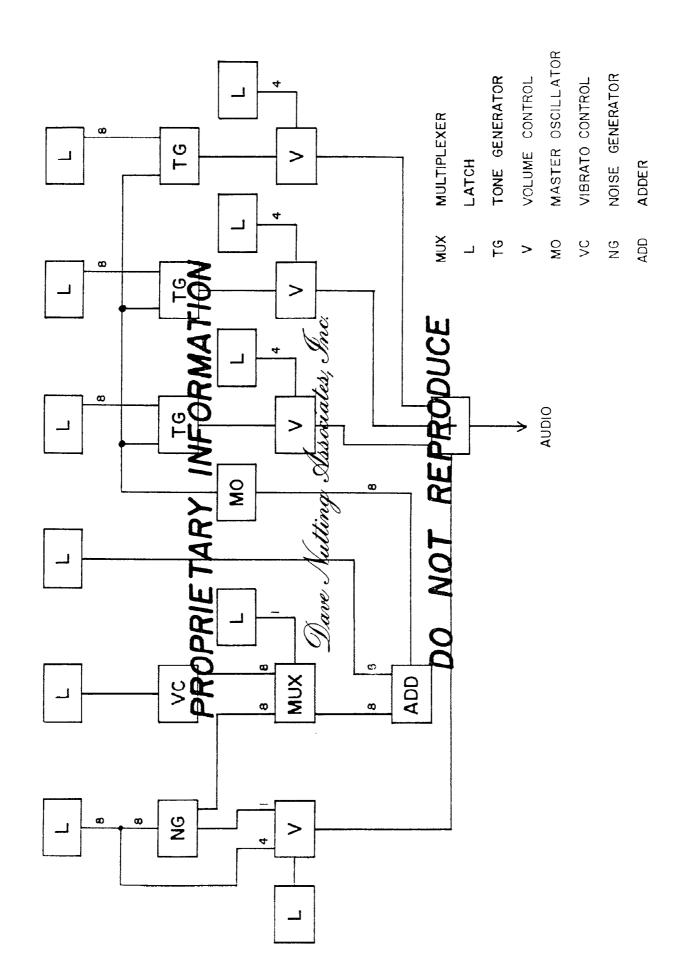

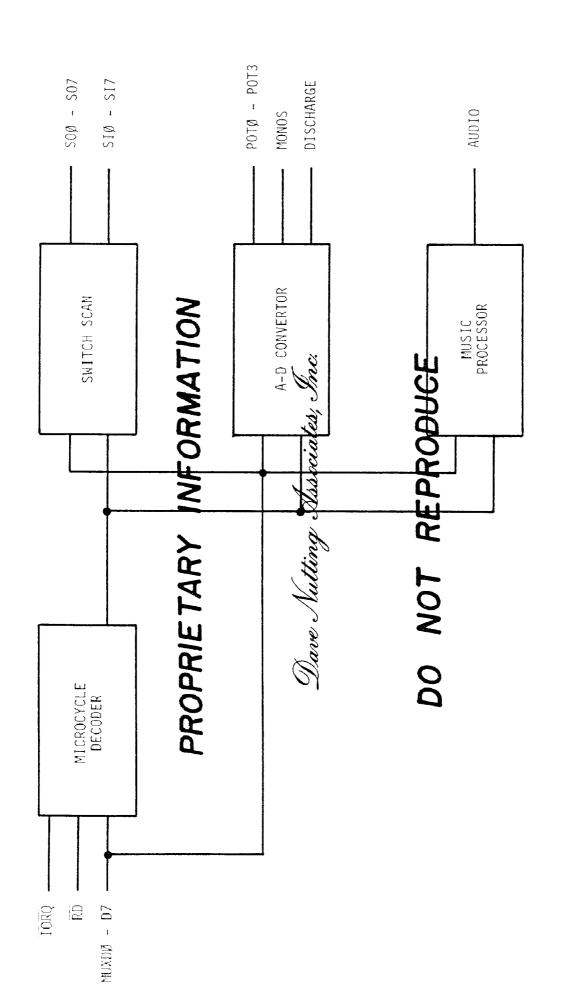

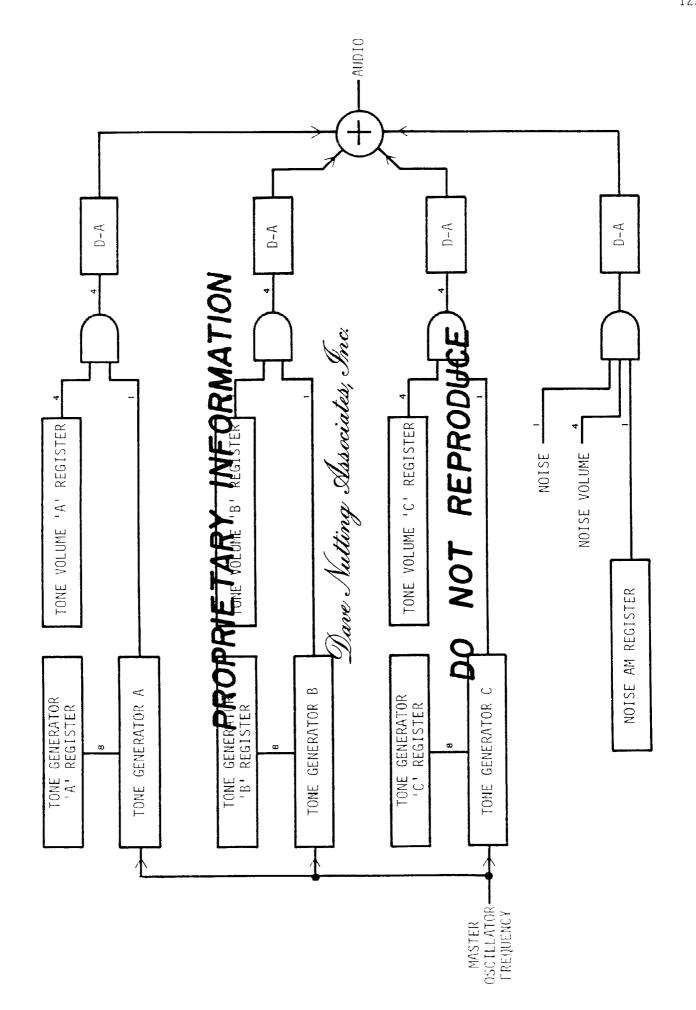

### MUSIC PROCESSOR

The music processor can be divided into two sections. The first section generates the Master Oscillator Frequency and the second section uses the Master Oscillator Frequency to generate tone frequencies and the analog audio output. The contracts of all registers in the Music Processor are set by output instructions from the  $Z-8\emptyset$ .

Master Oscillator Frequency is a square wave whose frequency is determined by the 8 binary inputs to the Master Oscillator. The 8-bit word is the sum of the contents of the Mux is controlled by Mux REG.

If MUX REG contains Ø, then data from the Vibrato System will be fed through the MUX. The two bits from the Vibrato Frequency Register determine the frequency of the square wave output of the Low Frequency Oscillator. The 6-bit and at the output of the AND gates oscillates between Ø and the contacts of the Vibrato Register. The frequency of oscillation is determined by the contents of the Vibrato Frequency Register. The 6-bit ward, along with two ground bits are fed through the MUX to the Adder. This causes the Master Oscillator Frequency to be modulated between two facuses thus giving a vibrato effect.

If MUX REG contains 1, then data from the Noise System will be fed through the MUX. The 8-bit word from the Noise Volume Register determines which bits from the Noise Generator will be present at the output of the AND gates.

If a bit in the Noise Volume Register is  $\emptyset$ , then the corresponding bit at the output of the AND gates will be  $\emptyset$ . If a bit in the Noise Volume Register is 1, then the corresponding bit at the output of the AND gates will be noise from the Noise Generator. This 8-bit word is sent through the MUX to the Adder. The Master Oscillator Frequency is modulated by noise.

In the second part of the Music Processor, the square wave from the Master Oscillator is fear to three Tone Generator circults which produce square waves at their out uts. The frequency of their outputs is determined by the contents of their Tone Generator Resister and Master Oscillator Frequency. The 4-bit words at the output of the AND gates oscillate between Ø and the contents of the Tone Volume Register. These 4-bit words are sent to D A Converters whose outputs oscillate between GND and a positive analyst voltage determined by the ontents of the Tone Volume Register.

One Noise bit and four worse Volume bits from the first section of the Music Processor are fed to a set of AND gates. This set of AND gates operates the same way at the AND gates for the tones except that the Noise AM Register must contain a 1 for the outputs of the AND gates to oscillate. The analog outputs of the four D-A Converters are summed to produce the single audio output.

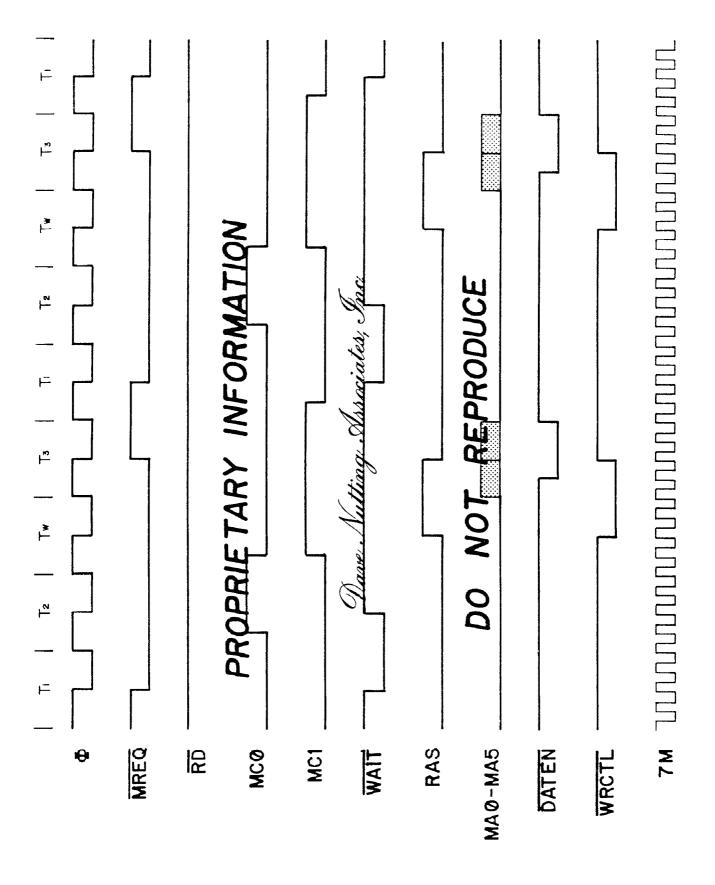

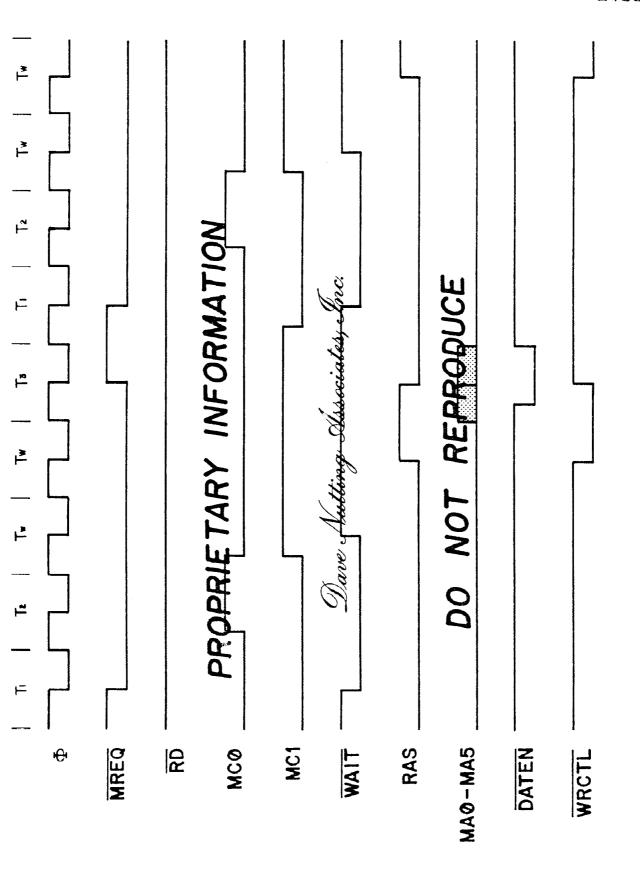

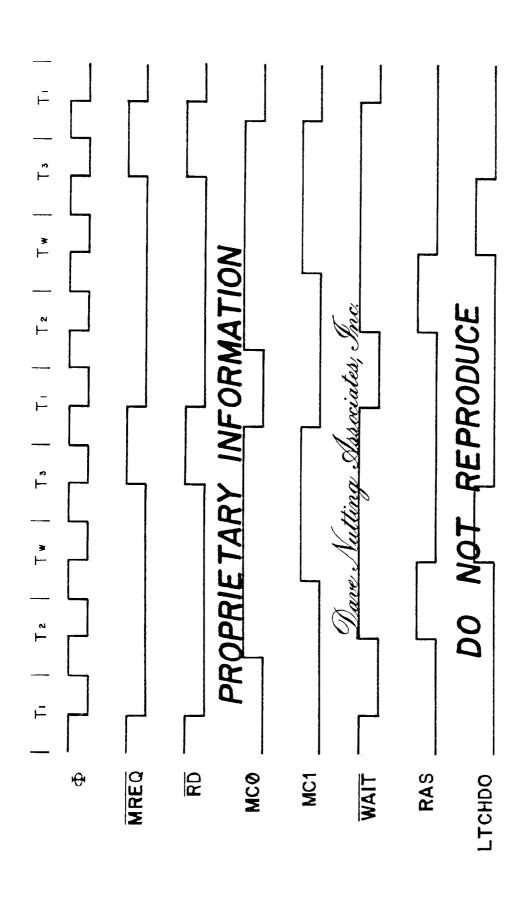

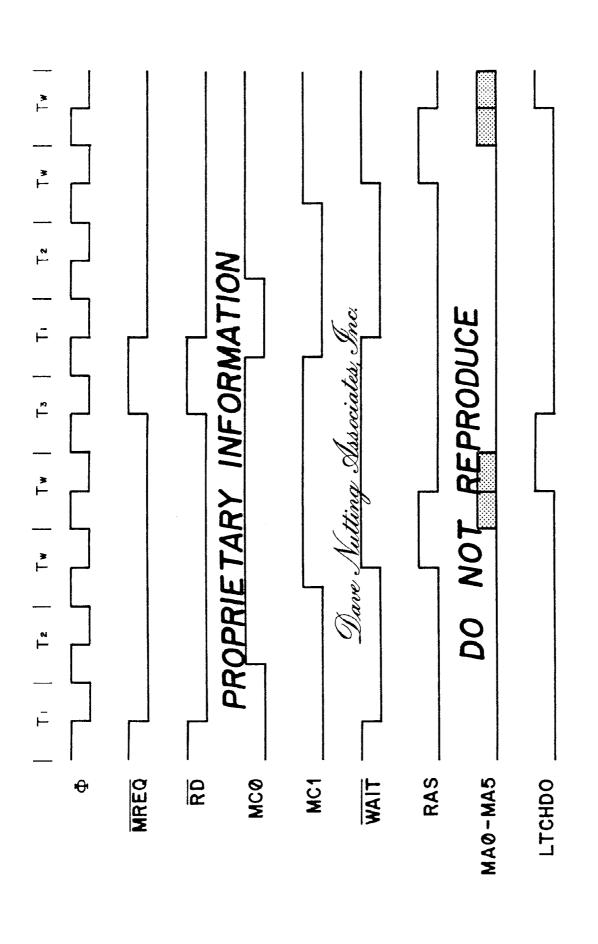

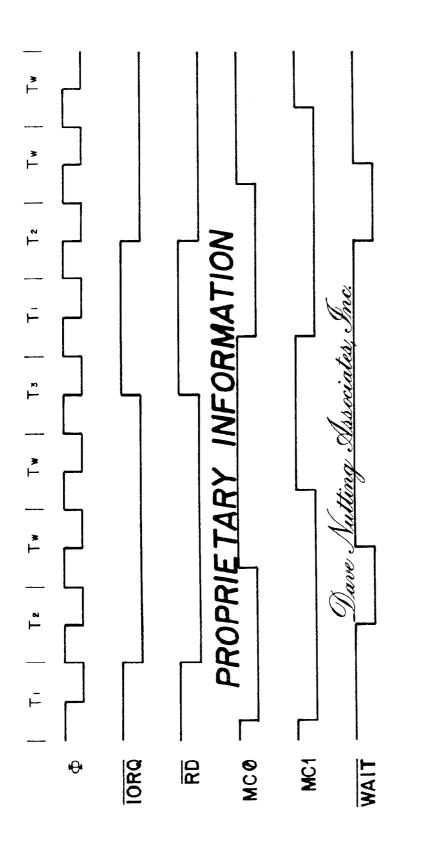

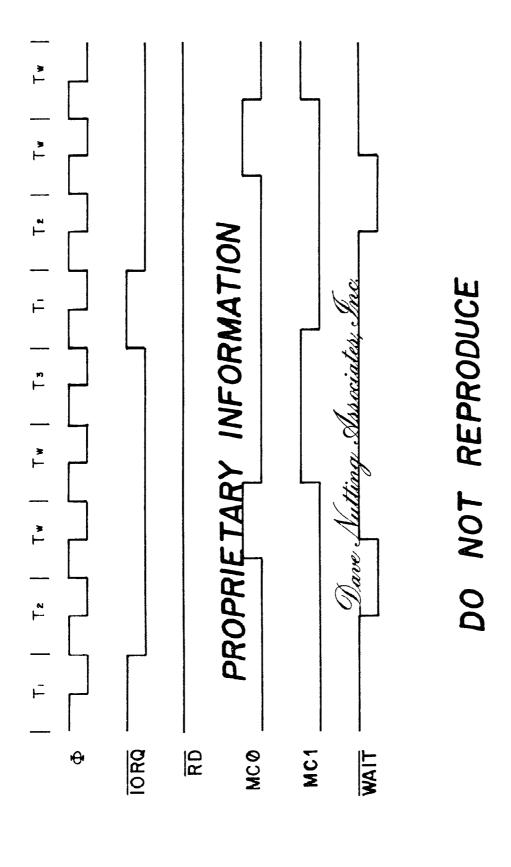

### CUSTOM CHIP TIMING

The following diagrams show the relationship of various signals in the system during different types of operations. Delays are shown to be zero nsec from the clock edge which causes the transition. The actual delay is even in "Electrical Specification for Midway Custom Circuits".

MUXDØ - MUXD7 is a  $\mathbb{R}^2$  it bidirectional address and tata bus for the custom chips. Busing this technique 16 bits of address and 8 bits of data can be sent to the custom chips on 8 wires. The state of the bus is determined by MC3 and MC1 from the data chip and  $\overline{\text{RFSH}}$  from the Z  $\mathbb{Z}^4$

| RFSH | MC1 | MCØ   | R A                       |

|------|-----|-------|---------------------------|

| L    | L   | AR)   | AØ - Aigto custom chips.  |

| L    | L   | ETAR  | AØ - A7 to custom ch      |

| L    | Н   | PRI   | AØ - Sto custom ch        |

| L    | Н   | ROPRI | AØ - A7 to custom chips   |

| Н    | L   |       | AØ - A7 to custom chips   |

| Н    | L   | Н     | A8 - A15 to custom chips  |

| Н    | Н   | L     | DØ - D7 to custom chips   |

| Н    | Н   | Н     | DØ - D7 from custom chips |

# MEMORY WRITE WITHOUT EXTRA WAIT STATE

# DO NOT REPRODUCE

# VIDEO TIMING

The frequency of  $\overline{PX}$  is half that of 7M and the  $\emptyset$  is one-fourth 7M. There are 455 cycles of 7M per horizontal line and 113 3/4  $\Phi$  cycles per line. Because of the extra 3/4 cycle  $\emptyset$  must be resynchronized at the beginning of  $\overline{PX}$  to line. This is done by stalling  $\emptyset$  for 3 cycles of 7M.  $\overline{PX}$  also stalled for the same amount of time. The timing relationship is shown below. The diagram also shows the relationship of  $\overline{PX}$  TDR to HORIZEDR. The two RES pulses shown are the first two vices RAS signals of a line, each line contains forty.

Dave Nutting Associa

PROPRIETARY INFOR

O NOT REI

BO NOT REPRODUCE. DR. JG. PX AND RAS

RELATIONSHIP BETWEEN HORIZ DR, HORIZ BLANK, HORIZ SYNC AND COLOR BURST  $\overline{M}$ SHADED AREA VOLTAGE DETERMINED BY THE DATA IN RAM EACH HORIZONTAL DIVISION IS EQUAL TO 312 CYCLES OF THE PATTERN REPEATS EVERY 455 CYCLES OF 7M

RELATIONSHIP BETWEEN VERTICAL SYNC, VERTICAL BLANK AND VERTICAL DRIVE EACH HORIZONTAL DIVISION REPRESENTS ONE HORIZONTAL SCAN

# ELECTRICAL SPECIFICATION FOR MIDWAY CUSTOM CIRCUITS

### I. GENERAL SYSTEM PARAMETERS

### I. A. Power Supplies

- 1. VDD=+5.0V <u>+</u>5%

- 2. VGG=+10.0V +5%

- 3. VSS=0.0V

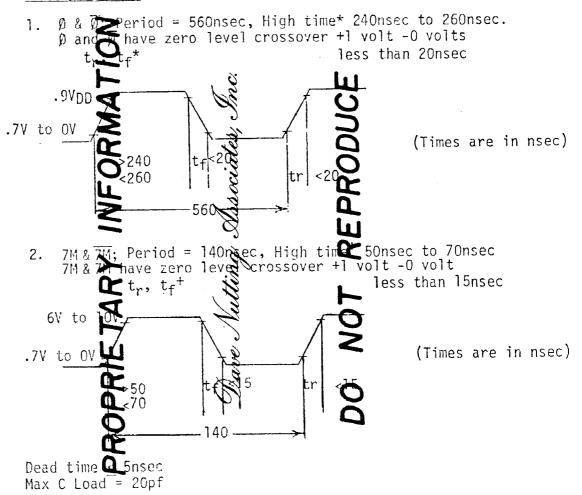

### I. B. Timing Signals

+Note

High time is time clock at > .6V.

2) Rise time from zero level to one level.

### I. B. (Continued)

### \*Note:

- 1. High time is time between 50% points.

- 2. Clock signals are generated by low power Shottky Logic (series 74LS). Full level swing on clock signals to be achieved through external resistor to VDD. Zero level .7V to OV.

- 3. Rise time from zero level to .9VDD.

# I. C. Z80 Data (MUXDØ-MUXD7)

- 1. Z80 D ta Bus interface requires a three-state output/input buffe. The three states are defined below.

- 2. Logic .5V + noise generated by thip, noise for address chip is .15% @ -430 $\mu A$

- 4. High ampedance: Leakage at either ogic 0 or 1 to be less than  $5\mu A$ .

- Transient Response: Transition from High Impedance to cor 1 will be complete within 442nsec if the 90% point of \$\overline{\rho}\$ of the last wait state of input eycle or 442nsec of the 90% point of \$\overline{\rho}\$ of the second wait state of the interrunt acknowledge cycle.

The maximum loss will be 80pf. This includes 14pfd for two custom chips.

- 6. Exception: The path chrough the Data chip connecting the RAM bus with the Z85 bus shall introduce a maximum of 160nsec of delay.

- 7. The landdress byte will be valid on the Z80 Data Bus at least 62nsec before  $\emptyset$ . The high address byte will be valid at least 79nsec before  $\widehat{\emptyset}$ . The data byte will be valid 55nsec before  $\widehat{\emptyset}$ .

# I. D. RAM Data Bus (MDO-MD7) - Home Game

- 1. The RAM Data Bus will require three state logic buffers.

- 2. Logic 0: .5V @ -25μA

- 3. Logic 1: 2.7V @ +25μA

- 4. High Impedance:  $5\mu A$  maximum leakage at either logic 0 or 1.

- 5. Transient Response: The outputs shall transition from High Impedance to 0 or 1 within 120nsec of 7M. The outputs shall transition from 1 or 0 to high impedance within 20nsec of 7M. Maximum load will be 20pf.

# I. E. RAM Data Dus (MDO-MD7) - Commercial Games

- 1. The RAData Bus will bequire three state logic buffers.

- 2. Logic 1: 2.7V @ +25μΑ

- 4. High Inedance: 5μΑ ximum leakage of either logic 0 or 1.

- 5. Transient Response: The output shall transition from High Insedance to 0 or 1 within 120nsec of 7M. The output shall transition from Nor 0 to High Impedance within 2nsec of 7M. Maximum load will be 10pf.

- I. F. Ambient operating temperature  $\geq 0^{\circ}$ C,  $\leq 2^{\circ}$ C.

- I. G. Storage tenserature  $\geq -65\%$ ,  $\leq 150^{\circ}$ C.

- I. H. Packing 4 in plastic.

II. CUSTOM CIRCUITOSPECIFICATION

This specification defines the terminal characteristics for each of the custom circuits. These specifications shall take precedence in case of conflict. All  $\emptyset$  references refer to the  $\emptyset$  and  $\overline{\emptyset}$  inputs to the address and I/O chip.

# II. A. Data Chip

| 1. | Input Pin List |     | <u>VO</u> (V) | <u>V1</u> | td (Low) <sup>1</sup> (nsec) | td (High) <sup>1</sup> (nsec) | <u>Ref</u> . |

|----|----------------|-----|---------------|-----------|------------------------------|-------------------------------|--------------|

|    | MREQ           |     | .5            | 2.45      | 132                          | .6                            | 7M           |

|    | RD             |     | .5            | 2.45      | 12                           | 6                             | 7M           |

|    | IORQ           |     | .5            | 2.45      | 112                          | 126                           | 7M           |

|    | 7M             | See | Sect          | ion I.B   |                              |                               |              |

|    | <del>7</del> M | 11  |               | 11        |                              |                               |              |

|    | WRCTL          |     | .5            | 3.1       | 82                           | 82                            | 7M           |

|    | Mī             |     | .5            | 2.45      | 12                           | 82                            | 7M           |

|    | LTCHDO         |     | .5            | 3.1       | 120                          | 120                           | 7M           |

|    | Serial 0       |     | .5            | 2.45      | 30                           | 30                            | 7M           |

|    | Seria          |     | .5            | 2.45      | 30                           | 30                            | 7 M          |

| 2. | Power Supplies |     | %             |           | 1.1                          |                               |              |

See Z80 Date Bus Spec. MXDO MXD1 MXD2 MXD3 MXD4 MXD5 MXD6 MXD7 MD0 MD1 RAM Data Bus Spec Seeon I.D. 11 See MD1 MD2 MD3 MD4 MD5 MD6 11 MD7

| 4.                | Outputs                                      | <u>VO</u> (V)                                  | $(\frac{10}{\mu A})$                   | <u>V1</u> (V)     | $(\frac{I1}{\mu A})$ | CAP<br>(pf)    | tp<br>(nsec)     | <u>Ref</u> .   |

|-------------------|----------------------------------------------|------------------------------------------------|----------------------------------------|-------------------|----------------------|----------------|------------------|----------------|

|                   | VIDEO*<br>R-Y*                               | *<br>*                                         |                                        |                   |                      | 10<br>10       | 100<br>600       | 7M             |

|                   | B-Y*<br>HORIZ DR<br>VERT_DR                  | *<br>Note 4<br>Note 4                          | 400<br>400                             | 2.7               | 20<br>20             | 10<br>20<br>20 | 600<br>20<br>20  | 7M<br>7M       |

|                   | 2.5V <sup>6</sup><br>Ø<br>PXCLK              | Note 4<br>Note 4                               | 400<br>400                             | 2.7               | 20<br>20             | 10<br>10       | DC<br>100<br>100 | 7M<br>7M       |

|                   | MCO<br>MC1<br>DATEN                          | Note 4<br>Note 4<br>Note 4                     | 400<br>400<br>400                      | 2.7<br>2.7<br>2.7 | 20<br>20<br>20       | 10<br>10<br>10 | 120<br>120<br>90 | 7M<br>7M<br>7M |

|                   | AT                                           | 1                                              | Juc.                                   | L                 | 2<br>1               |                |                  |                |

|                   | *Video                                       | Y, B-Y are                                     | agalog o                               | utputs            | <b>1</b> 40ns        | ec rate        | e. Video         | ),             |

|                   | must swit                                    | ch from 10%<br>3-Y transiti                    | %• <b>%</b> 0 90%<br>io <b>%</b> s not | to exc            | .d .6μse             | te in<br>c.    | 140nsec.         |                |

|                   | <b>\( \)</b>                                 | `                                              |                                        | i                 | 71                   |                |                  |                |

|                   | TARY II                                      |                                                | ıttin                                  | I                 | 0                    |                |                  |                |

| t <sub>d</sub> (  | (Low) and t                                  | d (High) is                                    | ₹<br>s <b>g</b> aximun                 | _                 |                      | xcept i        | where a          |                |

| min<br>For<br>Ser | imum is cho<br>IORQ R <b>a</b><br>ial O an S | own.<br>to Ø <sup>t</sup> d (La<br>Serial 1 wi | =132ns<br>Operat                       | sec td            | <u>(H</u> igh)=6r    |                |                  |                |

| .5٧               | + nois                                       | enerated by esistor cha                        | chip.                                  | 1                 |                      | 11 bec         | ome test         |                |

Tap on hot esistor chains for a capacitor. Will become test input with coltage applied > 8V.

The Z80 Ø generated by this signal with a clock driver which introduces a delay of <20nsec.

| II. B. I/O CH | hip |

|---------------|-----|

|---------------|-----|

| 1/0 | <u>Unip</u>                                                                                                           |                                                                              |                                                    |                                        |                                                      |                                                                    |

|-----|-----------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|----------------------------------------------------|----------------------------------------|------------------------------------------------------|--------------------------------------------------------------------|

| 1.  | Input Pin List                                                                                                        | <u>vo</u>                                                                    | <u>V1</u>                                          | Ref                                    | t <sub>d</sub> (High)<br>(nsec)                      | t <sub>d (Low)</sub> (nsec)                                        |

|     | Reset<br>MONOS<br>RD<br>IORQ<br>Ø                                                                                     | .5<br>Note<br>.5<br>.5<br>See Se                                             | 2.45                                               | ø or Ø<br>ø6<br>I.B.                   | 166<br>146 Ø                                         | 172 Ø or Ø<br>132 Ø                                                |

|     | S10<br>S11<br>S12<br>S13<br>S14<br>S15<br>S16<br>S17<br>TEST <b>W</b>                                                 | ciates, Fregis is is is                                                      | 3.3<br>3.3<br>3.3<br>3.3<br>3.3<br>3.3<br>5.0      | DUCE                                   |                                                      | Note 3<br>Note 3<br>Note 3<br>Note 3<br>Note 3<br>Note 3<br>Note 3 |

| 2.  | Power Supplies See Setion I.A.                                                                                        | g Associa                                                                    |                                                    | REPRODUCE                              |                                                      |                                                                    |

| 3.  | Bus Connections  MUXDO See Z80 [ MUXD1 "  MUXD2 "  MUXD4 "  MUXD4 "  MUXD4 "  MUXD5 "  MUXD6 "  MUXD6 "  MUXD7 "      | Dave Nustin                                                                  | Spec :                                             | Section I                              | . C.                                                 |                                                                    |

| 4.  | Ou tpu <b>Q</b>                                                                                                       | $\frac{VO}{(V)}$                                                             | $(\frac{I0}{\mu A})$                               | <u>V1</u><br>(V)                       | $(\frac{11}{\mu A})$                                 |                                                                    |

|     | Audio Note 4 Discharge Note 5 SOØ Note 3 SO1 Note 3 SO2 Note 3 SO3 Note 3 SO4 Note 3 SO5 Note 3 SO6 Note 3 SO7 Note 3 | Note 7<br>Note 7<br>Note 7<br>Note 7<br>Note 7<br>Note 7<br>Note 7<br>Note 7 | 7 200<br>7 200<br>7 200<br>7 200<br>7 200<br>7 200 | 4V<br>4V<br>4V<br>4V<br>4V<br>4V<br>4V | 1650<br>1650<br>1650<br>1650<br>1650<br>1650<br>1650 |                                                                    |

|     | POT Ø Note 2 POT 1 Note 2 POT 2 Note 2 POT 3 Note 2                                                                   |                                                                              | 5<br>5<br>5<br>5                                   | Vpp5<br>Vpp5<br>Vpp5<br>Vpp5           |                                                      |                                                                    |

- Note 1 MONOS triggers at 2.1 volts  $\pm 2\% \pm \text{noise}$  voltage when the supply is 5.25V.

- Note 2 Open source-Voltage measured with 0.2ma.

- Note 3 Time from load of address into microcycle register to date valid on MUX data bus from SI inputs (data path through address decoder, out on SO outputs, through closed switch and isolation diode, into SI input to MUX Data Bus) shall be 2μsec max. Drop of isolation diode will be 0.7V max. SO must drive 2kΩ in the high level. Max C load of SO hall be 300 pf. SI input shall have kill device habled by INPUT.

- Note 4 Audio voltage oscillates between OV and one of the rollowing voltages; .33, .67  $\square$  .00, 1.33, 1.67, 2.00, 33, 2.67, 3.88, 3.33, 3.67  $\square$  .00, 4.33, 4.67 and 00. These voltages should be  $\pm 6\%$ . The load shall be 1000pf and  $\pm 100$ k $\Omega$ .

- Note 5 Discharge is open drain to VS Discharges .01µfd capacitor to .2% in 144µsec.

- Note 6 Or  $\overline{IOREQ}$  Ref.  $0 \ \overline{p}$  td (Low)=152nsec td (High)=166nsec.

# II. C. Address Chip

| 1. | Input Pin List                                                               | $\frac{V0}{V}$                         | ( <u>V)</u>                                         | tpd (Low)<br>(nsec)                                  | t <sub>pd (High)</sub><br>(nsec)                              | REF                                      |

|----|------------------------------------------------------------------------------|----------------------------------------|-----------------------------------------------------|------------------------------------------------------|---------------------------------------------------------------|------------------------------------------|

|    | RFSH<br>MREQ<br>RD<br>MI<br>A121<br>A131<br>A141                             | .55.55.55.55.55                        | 2.45<br>2.45<br>2.45<br>2.45<br>2.45<br>2.45        | 222 <u>Ø</u><br>152 <u>Ø</u><br>172 Ø or<br>176 Ø    | 216<br>166<br>Ø 166<br>242                                    | g or g g g g g g g g g g g g g g g g g g |

|    | A151<br>IORQ<br>LIGHT ON<br>TEST OR.<br>HORIZ. DR.<br>VERT. DR.              | 55555555555555555555555555555555555555 | 2.45<br>2.45<br>2.45<br>2.45<br>5.0<br>2.45<br>2.45 | 132 Ø<br>Asyn<br>DC<br>Note 3<br>Note 4              | 146                                                           | 0<br>0<br>0<br>2<br>0<br>0               |

| 2. | Power Opplies See See on I.A.                                                | Issociates, e                          |                                                     | りつつとし                                                |                                                               |                                          |

| 3. | Bus Commections                                                              | S Br                                   | C                                                   | <b>K</b>                                             |                                                               |                                          |

|    | MXD0<br>MXD1<br>MXD2<br>MXD3<br>MXD4<br>MXD5<br>MXD6<br>MXD7<br>MXD7<br>MXD7 | Dave Musti                             | (                                                   | *ion I.E.                                            |                                                               |                                          |

| 4. | Output VO I (V) (µ.  LATCHDO Note 7 No WAIT 4  MAO-MA5 " 4  RASO-RAS3 " 4    |                                        | <u> 11                                    </u>      | AP tpd(Low) pf) (nsec) 0 280 5 490 0 242 5 490 0 382 | tpd(High)<br>(nsec)<br>140<br>490<br>240<br>572<br>382<br>382 | REF                                      |

- 1. Time from High Impedance to 1 or 0 is 200nsec. (from  $\emptyset_1$  of  $T_1$ )

- 2. For IORQ Ref to ptd (Low)=152nsec td (High)=166nsec. p

3. Horizontal Drive time from low to high is 40nsec after  $\overline{\emptyset}$ . Time from high to low is 100nsec before rising edge of  $\emptyset$ .

- 4. Vertical Drive will transition from low to high 40nsec after falling edge of  $\emptyset$ . Its width will be 2.1 usec max. 1.54usec min. It will go from high to low 100nsec before falling edge of  $\emptyset$ .

- 5. Reference tpd (High) is Ø.

- 6. MOS to MOS signal.

- 7. .5V  $\pm$  noise deperated by Address Chin ( 15V)  $\pm$  65V

# III. I/O MODE DECODE

. 2F

# I/O Parts

| <u>HEX</u>                                                                                     | <u>Out</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Input                                                                                      |

|------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|

| 0<br>1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>A<br>B<br>C<br>D<br>E<br>F<br>10<br>11<br>12 | Color Ø Right " 1 " " 2 " " 3 " " 0 Left " 1 " " 2 " " 3 " Obnsumer/Commercial Horiz Color Bndry Vertical Blank Tolor Block T Gric Reg Hiterrupt Feedback Therrupt Mode Therrupt Line. Tone Master OSC Tremello Tone A,B Volume | Intercept Feedback  Ver Cal Addr Feedback Hor Cantal Addr Feedback SW Cak 0  1 2 3 4 5 6 7 |

| 24                                                                                             | PROPR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | POT O " " " " " "                                                                          |

| 23                                                                                             | PR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                            |